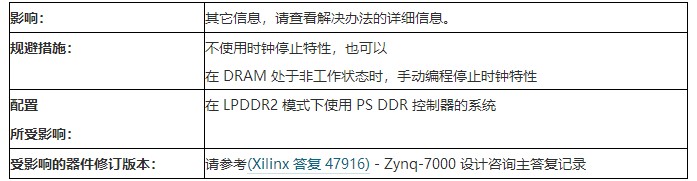

description When the transaction queue is empty, the controller will properly stop the clock, but when the clock restarts, the controller will quickly issue DRAM transactions. It cannot recognize the tXP timing parameter value. Either do not use the LPDDR2 clock stop feature, or provide software to ensure that the clock stop enable / disable is completed only when there is no DRAM activity. solution When clock_phy_stop is enabled for LPDDR2, if the transaction queue is empty, the controller will properly stop the DRAM clock. Before restarting the clock, you should wait for tXP plus two clock cycles (about five clock cycles), but this is not the case. If the transaction queue gets a new transaction before the required delay period, the LPDDR2 clock may restart too fast. Solution details: If the clock stop feature is required, the software must stop the clock by asserting the reg_ddrc_clock_stop_en bit. The software must take care to perform this task only when it is determined that there is no traffic on the host interface. The software must wait tXP + for two clock cycles before re-enabling the clock. SHENZHEN CHONDEKUAI TECHNOLOGY CO.LTD , https://www.szfourinone.com

The dynamic clock stops restarting too quickly, which can be solved by programming the LPDDR2 controller

When there is no memory transaction execution and if a memory request is received to restart the clock, the user can program the LPDDR2 controller to stop the DRAM clock.